# HA-5020 SPICE Macromodel (CFA)

Application Note

May 1996

MM5020.3

### Introduction

The HA-5020 is a low cost single amplifier optimized for RGB video applications and gains between 1 and 10. It is a current feedback amplifier; thus it yields less bandwidth degradation at high closed loop gains than voltage feedback amplifiers. The HA-5020 also features a disable function that significantly reduces supply current while forcing the output to a true high impedance state. The macromodel for the HA-5020 is PSPICE (registered trademark of MicroSim Corp.) compatible, and may be compatible with other simulation programs as well. The model file is in ASCII format and may be viewed/edited with any text editor.

All models require a trade-off between accuracy and complexity (simulation time). Intersil's models emulate the nominal performance of a typical device, and are designed to match the typical performance curves in the device data sheet.

SPICE simulations should not be considered a substitute for breadboarding a circuit; rather, they should be used to select preliminary component values and to verify the validity of a design approach.

Do not rely on simulations to predict device performance when deviating from the operating conditions specified in the data sheet (e.g. just because the model works with  $\pm$ 1V supplies, don't assume that the actual amplifier does). Instead, refer to the data sheet performance curves, or call the factory for assistance (321-724-7143).

The HA-5020 model is configured as a subcircuit for easy incorporation into larger circuit files. When using PSPICE, call a subcircuit from the top level circuit file by adding a .LIB statement to point to the file containing the subcircuit (e.g. .lib c:\models\ha5020.cir), and by including a subcircuit call of the following form:

xname +IN -IN V+ V- OUT ENABLE model name (e.g. x22 101 111 113 114 112 110 HA5020)

Note that the node order in the subcircuit call follows the industry standard, and the order is also documented in the comment section at the beginning of the model file.

## Model Description

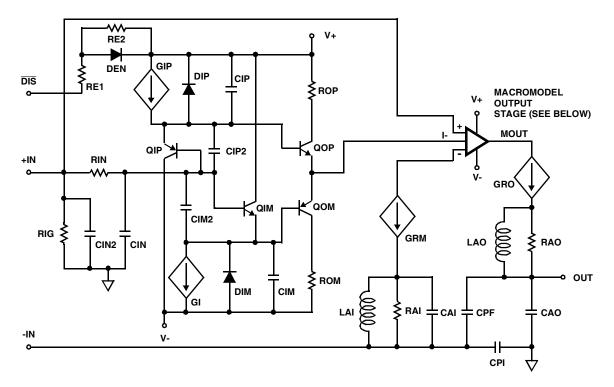

The macromodel schematic is shown in Figure 1, and the PSPICE listing for the macromodel follows. The model topology consists of three main functional sections: a buffer between the two input pins, an output section between the negative input pin and the output pin, and an enable section.

The topology of the input buffer section is a basic four transistor voltage follower. This configuration was used in order to efficiently model the Enable capability of the amplifier. Additional components are added to this structure in order to model the critical characteristics of the actual amplifier. Of these additional components, some are used to model both the slew limiting of the negative input and the fractional step feed-through from the positive input to the negative input. Other elements model the voltage and current limiting of the negative input. The bias current of the positive input and the high frequency voltage gain are also accounted for in the input buffer section model.

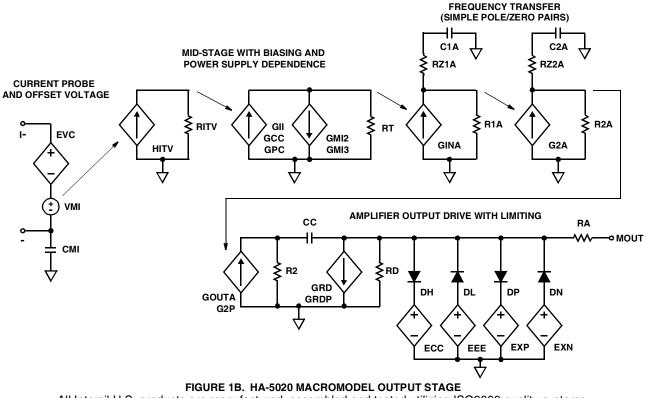

The output section is a transimpedance amplifier constructed from four stages: current probe, mid stage, frequency transfer, and output drive. The current probe stage monitors the current through the negative input pin and also models the input offset voltage. The mid stage is used for the bias current of the negative input and for power supply gains. This stage is also used to capture the operation of the output transimpedance amplifier while disabled. The frequency transfer block consists of two poles and two zeros for modelling the high frequency open-loop transimpedance gain. The output drive stage accounts for several characteristics including: the output slew limits and resulting transimpedance gain bandwidth product, the saturation delay times, and the voltage and current limiting at the output.

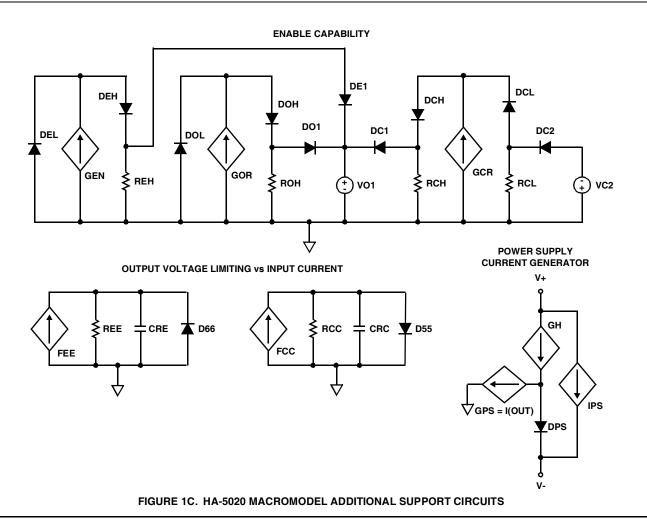

The enable section of the model is used to control certain characteristics of other blocks in the model. This section operates according to the voltage level at the enable input pin and to the status of the output pin. Two characteristics of the output which are controlled by this section are the impedance and slew limiting. The internal bias currents of the input buffer section are also set by the enable section. As a result, high impedance states are achieved at the two input pins whenever the amplifier is disabled.

In addition to the three main functional sections, smaller constructs and individual components are used to model other important amplifier characteristics. Specifically, one section is used to capture the change in the voltage limits of the output as a function of the current through the negative input. Power supply currents are also modelled with an additional section. At each amplifier pin, several individual components are included to model high frequency impedance characteristics, including any significant package parasitics.

The model is optimized for operation at  $\pm$ 5V, but it operates over the full range of supply voltages. Beware, the model does not simulate various breakdown conditions such as exceeding the maximum ratings, but it does have input limiting. The model does not include input voltage or current noise, or temperature effects.

The poles and zeros of the transimpedance frequency transfer section have been located with great care to insure that the performance for 3 different inverting and non-inverting gains is matched closely to the curves given in the data sheet. Also, the pole/zero placement insures that the transient response matches that shown in the data sheet.

All Intersil U.S. products are manufactured, assembled and tested utilizing ISO9000 quality systems. Intersil Corporation's quality certifications can be viewed at www.intersil.com/design/quality

Intersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design, software and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see www.intersil.com

## HA-5020 SPICE Macromodel Listing

```

.SUBCKT HA5020 101 111 113 114 112 110

LAO 115 112 250N

RAO 115 112 125

CAO 112 0 4P

LAI 116 111 40N

RAI 116 111 200

CAI 116 111 3P

CPI 111 0 1.5P

CPF 112 111 2.5P

.MODEL QIP PNP IS=1.0E-16 BF=130 NF=2.2

.MODEL QIM NPN IS=1.0E-16 BF=220 NF=2.5

.MODEL QOP NPN IS=1.0E-16 BF=180 NF=2.2

.MODEL QOM PNP IS=1.1E-16 BF=50 NF=2.5

ROP 113 117 +3.5000000E+02

QOP 117 118 119 QOP

CIP2 120 118 +2.73661972E-13

CIP 113 118 +6.7000000E-13

DIP 118 113 DLIM

GIP 113 118 121 0 +3.3500000E-04

DIPL 114 118 DLIM

QIP 114 120 118 QIP

```

HA-5020 SPICE Macromodel Listing (Continued)

RIN 101 120 280 CIN2 101 0 .03P RIG 101 0 +2.6000000E+07 CIN 120 0 .5PF QIM 113 120 122 QIM GIM 122 114 121 0 +3.3500000E-04 DIML 122 113 DLIM DIM 114 122 DLIM CIM 122 114 +6.29914530E-13 CIM2 120 122 +3.24501425E-13 QOM 123 122 119 QOM ROM 123 114 +3.5000000E+02 .MODEL DLIM2 D N=.01 IS=1E-10 RE1 110 124 15K RE2 124 113 15K DEN 124 113 DEN .MODEL DEN D BV=+5.26 IBV=1.0E-10 VMI 102 108 +0.0000000E+00 EVC 119 108 POLY 4 101 0 102 0 113 0 114 0 -2.13000009E-03 +3.09210000E-04 ++3.09210000E-04 -3.15209991E-04 -3.03210009E-04 0 0 -1.88100000E-06 ++1.88100000E-06 0 -1.88100000E-06 +1.88100000E-06 +1.88100000E-06 0 +-1.8810000E-06 CMI 102 0 +1.0000000E-16 HITV 0 125 VMI 1 RITV 125 0 1 GII 0 126 POLY 2 121 0 125 0 0 0 0 0 -1.97000000E-03 GCC 0 126 POLY 5 121 0 101 0 102 0 113 0 114 0 0 +7.80927711E-09 0 0 0 0 0 ++2.78640749E-11 +2.78640749E-11 +3.49558407E-11 +2.07723091E-11 0 0 0 0 0 0 +0 0 0 0 0 0 0 0 0 0 0 -1.92087022E-16 +1.92087022E-16 0 -1.92087022E-16 ++1.92087022E-16 +1.92087022E-16 0 -1.92087022E-16 RT 126 0 +1.0000000E+00 GPC 0 126 POLY 3 121 0 113 0 114 0 0 0 0 0 0 +0.0000000E+00 +0.0000000E+00 R1A 127 0 +2.14285714E+03 RZ1A 127 128 -1.14285714E+03 C1A 128 0 +7.95798186E-13 GINA 0 127 126 0 +4.66666667E-04 R2A 129 0 +2.25000000E+03 RZ2A 129 130 -1.25000000E+03 C2A 130 0 +3.18319274E-13 G2A 0 129 127 0 +4.4444444E-04 GOUTA 106 0 129 0 -1.00000000E+00 GRD 104 0 106 0 +1.02164070E+01 G2P 0 106 POLY 2 113 0 114 0 0 +3.46573590E-07 +3.46573590E-07 GRDP 104 0 POLY 2 113 0 114 0 0 -5.10970951E+00 -5.10970951E+00 R2 106 0 +1.44269504E+06 CC 106 104 +1.0000000E-14 RD 104 0 +3.32000000E+02 RA 104 109 +8.0000000E+00 DH 104 100 DH +1.0000000E+00 DL 131 104 DL +1.0000000E+00 .MODEL DH D IS=+2.16387643E-14 N=.2

HA-5020 SPICE Macromodel Listing (Continued) .MODEL DL D IS=+6.45488179E-15 N=.2 ECC 100 0 POLY 2 113 0 132 0 -1.1000000E+00 1 1 EEE 131 0 POLY 2 114 0 133 0 +1.13500000E+00 1 1 FCC 0 132 POLY 1 VMI -1.30520000E-04 +1.30000000E-01 RCC 132 0 1K CRC 132 0 +1.0000000E-10 D55 132 0 DLIMVO FEE 0 133 POLY 1 VMI +2.19120000E-04 +2.20000000E-01 REE 133 0 1K CRE 133 0 +1.0000000E-10 D66 0 133 DLIMVO .MODEL DLIMVO D N=.01 IS=1E-20 DP 104 134 DCL +1.0000000E+00 EXP 134 0 POLY 2 104 0 109 0 0 -1.75393075E-01 +1.17421768E+00 DN 107 104 DCL +1.0000000E+00 EXN 107 0 POLY 2 104 0 109 0 0 +8.82115687E-02 +9.09643047E-01 .MODEL DCL D IS=1E-9 N=1 IPS 113 114 +5.78000000E-03 GPS 135 0 104 109 +1.25000000E-01 GH 113 135 POLY 1 135 114 +1.52098765E-02 -3.04197531E-02 +2.28148148E-02 +-7.60493827E-03 +9.50617284E-04 DPS 135 114 DPS .MODEL DPS D IS=1E-16 N=+3.40657494E+00 GEN 0 136 POLY 3 110 0 113 0 114 0 +4.00000000E+00 +1.00000000E+00 +-1.0000000E+00 +0.0000000E+00 DEH 136 121 DLIM REH 121 0 1K DE1 121 137 DLIM VO1 137 0 0.99 **DEL 0 136 DLIM** .MODEL DLIM D N=.01 IS=1E-20 GRM 102 116 POLY 2 102 116 121 0 0 0 0 0 +1.42857143E+01 GMI2 126 0 POLY 2 104 0 121 0 0 +2.04356846E-10 0 0 -2.04356846E-10 GOR 0 138 POLY 3 109 0 115 0 121 0 -6.40000000E-01 0 0 +1.28000000E+00 1 -2 +0.1DOH 138 139 DLIM ROH 139 0 1K DO1 139 137 DLIM **DOL 0 138 DLIM** GRO 109 115 POLY 2 109 115 139 0 0 0 0 0 +1.25000000E+01 GCR 0 140 POLY 3 0 140 121 0 104 109 0 0 0 +1.25000000E+01 0 100 DCH 140 141 DLIM RCH 141 0 +8.0000000E+04 DC1 141 137 DLIM DCL 142 140 DLIM RCL 142 0 +8.0000000E+04 DC2 143 142 DLIM VC2 0 143 0.99 GMI3 126 0 POLY 3 121 0 141 0 0 142 0 0 -1.10000000E-08 +1.60000000E-08 0 ++1.1000000E-08 -1.6000000E-08 .ENDS HA5020

#### HA-5020 Macromodel Performance

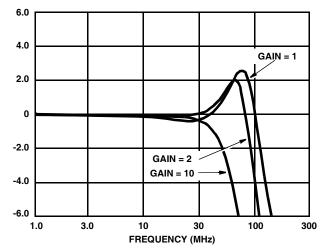

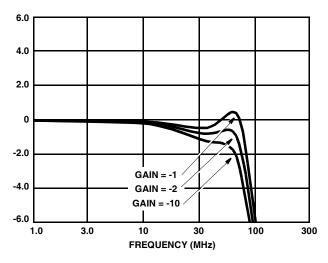

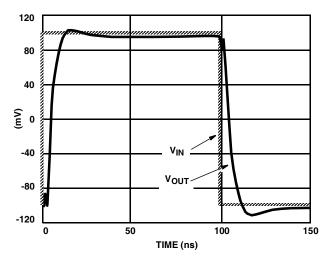

Intersil application note AN9523 titled "Evaluation Programs For SPICE Op Amp Models" was used as a guideline for evaluating the HA-5020 performance. Figure 2 shows the noninverting AC transfer function. In the gain of one configuration the peaking is 2.5dB versus the 3.2dB of peaking shown in the data sheet. The -3dB bandwidth is 125MHz in both cases. This is quite good correlation between the model and the data sheet. Similarly, the non-inverting gains of 2 and 10 closely match the data sheet transfer functions. In all cases the data sheet conditions were met during the SPICE analysis; i.e.,  $R_F = 1k\Omega$ ,  $R_I = 400\Omega$ ,  $V_{SUPPLY} = \pm 5V$ , and  $C_I = 10pF$ . The inverting AC transfer function is shown in Figure 3. Notice that in the gain of -1 configuration the peaking is 0.5dB versus the 1.5dB of peaking shown on the data sheet, and that the gain of -2 and -10 curves match those shown in the data sheet. Again the correlation between the model and the data sheet is guite good. The small signal pulse response is shown in Figure 4 and the rise time, fall time, propagation delay, and time domain peaking can be read off this waveform.

FIGURE 2. HA-5020 NON-INVERTING OP AMP AC TRANS-FER FUNCTION

FIGURE 3. HA-5020 INVERTING OP AMP AC TRANSFER FUNCTION

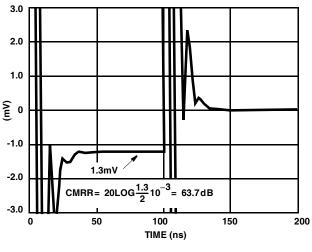

The common mode rejection ratio is obtained through the use of two identical amplifiers and the equation CMRR = common mode input voltage divided by the differential input voltage for a constant output voltage (see Figure 5). The input for this test is chosen as a 2V square wave. This enables the evaluation of the worst case CMRR.

FIGURE 4. HA-5020 SMALL SIGNAL PULSE RESPONSE

FIGURE 5. HA-5020 CMRR

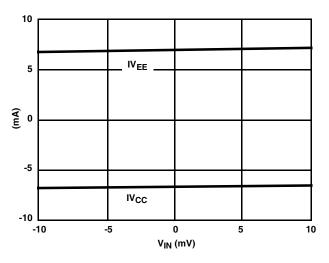

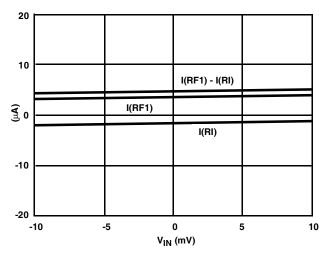

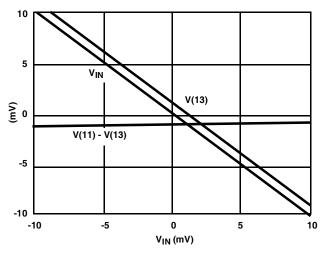

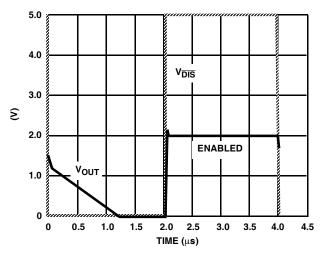

Figures 6, 7, and 8 show the salient DC parameters for the HA-5020. The input signal for this test is a DC sweep which enables the evaluation of parameters around zero. The response to a stimulus on the DIS input is shown in Figure 9. The op amp is configured as a non-inverting follower circuit with a DC input of 2V. The DIS pin voltage is switched from ground to  $V_{CC}$  to switch the op amp on and off. The slower turn-off time is seen in the figure along with the much faster turn-on time.

FIGURE 6. HA-5020 POWER SUPPLY CURRENT DRAIN

FIGURE 7. HA-5020 INPUT CURRENT

FIGURE 8. HA-5020 INPUT OFFSET VOLTAGE

7

FIGURE 9. HA-5020 ENABLE/DISABLE RESPONSE TIME

#### Summary

The macromodel performs well for both the DC and AC parameters. It is a fraction of a dB off for some AC tests, but this is acceptable for an approximation. At least the model has peaking where the op amp has peaking, and the response for different gains is modeled correctly. The model is just an approximation! It cannot predict performance to a few percent; especially when one considers that the circuit layout parameters have such a large effect on high frequency performance. The model will not predict the actual performance in many circumstances such as non-linearities, limits of performance, or extended range operation. Only testing will confirm performance out of the normal operating range, and all circuits should be tested to confirm the model's predictions.

#### License Statement

The information in these SPICE macromodels (models) is protected by the United States copyright laws. Intersil Corporation (Intersil) hereby grants users of these models, herein referred to as licensee, a nonexclusive, nontransferable license to use these models as long as the licensee abides by the terms of this agreement. Before using the models, the licensee should read this license and accept the terms.

The licensee may not sell, loan, rent, lease, or license the models, in whole, in part, or in modified form, to anyone outside the licensee's company. The licensee may modify these models to suit his specific application.

These models are provided "AS IS, WHERE IS, AND WITH NO WARRANTY OF ANY KIND EITHER EXPRESSED OR IMPLIED, INCLUDING BUT NOT LIMITED TO ANY IMPLIED WARRANTIES OF MERCHANTABILITY AND FIT-NESS FOR A PARTICULAR PURPOSE." In no event will Intersil be liable for special, collateral, incidental, or consequential damages in connection with or arising out of the use of these models. Intersil reserves the right to make changes to the products and the models without prior notice.